डेटा सेंटर का DDR5 में माइग्रेशन अन्य अपग्रेड की तुलना में अधिक महत्वपूर्ण हो सकता है।हालाँकि, बहुत से लोग अस्पष्ट रूप से सोचते हैं कि DDR5 DDR4 को पूरी तरह से बदलने के लिए एक संक्रमण मात्र है।DDR5 के आगमन के साथ प्रोसेसर अनिवार्य रूप से बदल जाएंगे, और उनमें कुछ नया होगायादइंटरफ़ेस, जैसा कि SDRAM से DRAM अपग्रेड की पिछली पीढ़ियों के मामले में थाडीडीआर4.

हालाँकि, DDR5 केवल एक इंटरफ़ेस परिवर्तन नहीं है, यह प्रोसेसर मेमोरी सिस्टम की अवधारणा को बदल रहा है।वास्तव में, DDR5 में परिवर्तन एक संगत सर्वर प्लेटफ़ॉर्म पर अपग्रेड को उचित ठहराने के लिए पर्याप्त हो सकते हैं।

नया मेमोरी इंटरफ़ेस क्यों चुनें?

कंप्यूटर के आगमन के बाद से कंप्यूटिंग समस्याएं और अधिक जटिल हो गई हैं, और इस अपरिहार्य वृद्धि ने सर्वरों की अधिक संख्या, लगातार बढ़ती मेमोरी और स्टोरेज क्षमता, और उच्च प्रोसेसर घड़ी की गति और कोर गिनती के रूप में विकास को प्रेरित किया है, लेकिन वास्तुशिल्प परिवर्तनों को भी प्रेरित किया है। , जिसमें हाल ही में अलग-अलग और कार्यान्वित एआई तकनीकों को अपनाना शामिल है।

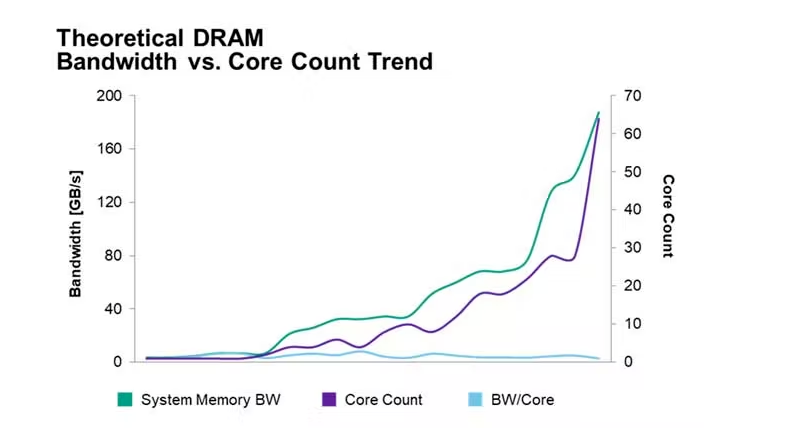

कुछ लोग सोच सकते हैं कि ये सब एक साथ हो रहा है क्योंकि सभी संख्याएँ बढ़ रही हैं।हालाँकि, जबकि प्रोसेसर कोर की संख्या में वृद्धि हुई है, डीडीआर बैंडविड्थ ने गति नहीं रखी है, इसलिए प्रति कोर बैंडविड्थ वास्तव में कम हो रही है।

चूंकि डेटा सेट का विस्तार हो रहा है, विशेष रूप से एचपीसी, गेम्स, वीडियो कोडिंग, मशीन लर्निंग रीजनिंग, बड़े डेटा विश्लेषण और डेटाबेस के लिए, हालांकि सीपीयू में अधिक मेमोरी चैनल जोड़कर मेमोरी ट्रांसफर की बैंडविड्थ में सुधार किया जा सकता है, लेकिन इससे अधिक बिजली की खपत होती है .प्रोसेसर पिन गिनती भी इस दृष्टिकोण की स्थिरता को सीमित करती है, और चैनलों की संख्या हमेशा के लिए नहीं बढ़ सकती है।

कुछ एप्लिकेशन, विशेष रूप से हाई-कोर सबसिस्टम जैसे जीपीयू और विशेष एआई प्रोसेसर, एक प्रकार की हाई-बैंडविड्थ मेमोरी (एचबीएम) का उपयोग करते हैं।प्रौद्योगिकी 1024-बिट मेमोरी लेन के माध्यम से स्टैक्ड DRAM चिप्स से प्रोसेसर तक डेटा चलाती है, जिससे यह AI जैसे मेमोरी-गहन अनुप्रयोगों के लिए एक बेहतरीन समाधान बन जाता है।इन अनुप्रयोगों में, तेजी से स्थानांतरण प्रदान करने के लिए प्रोसेसर और मेमोरी को जितना संभव हो उतना करीब होना चाहिए।हालाँकि, यह अधिक महंगा भी है, और चिप्स बदली/उन्नयन योग्य मॉड्यूल पर फिट नहीं हो सकते हैं।

और DDR5 मेमोरी, जिसे इस वर्ष व्यापक रूप से रोल आउट किया जाना शुरू हुआ, अपग्रेडेबिलिटी का समर्थन करते हुए प्रोसेसर और मेमोरी के बीच चैनल बैंडविड्थ को बेहतर बनाने के लिए डिज़ाइन किया गया है।

बैंडविड्थ और विलंबता

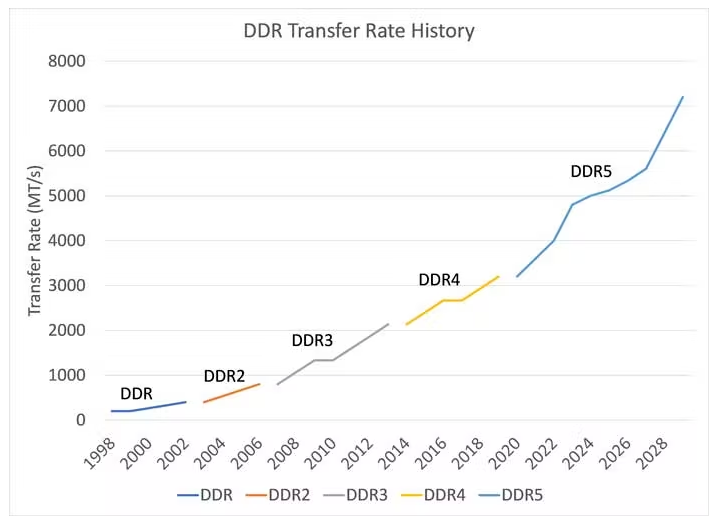

DDR5 की स्थानांतरण दर DDR की किसी भी पिछली पीढ़ी की तुलना में तेज़ है, वास्तव में, DDR4 की तुलना में, DDR5 की स्थानांतरण दर दोगुनी से भी अधिक है।DDR5 साधारण लाभ पर इन स्थानांतरण दरों पर प्रदर्शन को सक्षम करने के लिए अतिरिक्त वास्तुशिल्प परिवर्तन भी पेश करता है और देखी गई डेटा बस दक्षता में सुधार करेगा।

इसके अतिरिक्त, बर्स्ट की लंबाई BL8 से दोगुनी करके BL16 कर दी गई, जिससे प्रत्येक मॉड्यूल में दो स्वतंत्र उप-चैनल हो गए और सिस्टम में उपलब्ध चैनल अनिवार्य रूप से दोगुना हो गए।न केवल आपको उच्च स्थानांतरण गति मिलती है, बल्कि आपको एक पुनर्निर्मित मेमोरी चैनल भी मिलता है जो उच्च स्थानांतरण दर के बिना भी DDR4 से बेहतर प्रदर्शन करता है।

मेमोरी-सघन प्रक्रियाओं को DDR5 में परिवर्तन से भारी बढ़ावा मिलेगा, और आज के कई डेटा-सघन कार्यभार, विशेष रूप से AI, डेटाबेस और ऑनलाइन लेनदेन प्रसंस्करण (OLTP), इस विवरण में फिट बैठते हैं।

संचरण दर भी बहुत महत्वपूर्ण है.DDR5 मेमोरी की वर्तमान गति सीमा 4800~6400MT/s है।जैसे-जैसे प्रौद्योगिकी परिपक्व होगी, ट्रांसमिशन दर अधिक होने की उम्मीद है।

ऊर्जा की खपत

DDR5, DDR4 की तुलना में कम वोल्टेज का उपयोग करता है, अर्थात 1.2V के बजाय 1.1V।हालाँकि 8% का अंतर बहुत अधिक नहीं लग सकता है, लेकिन जब बिजली खपत अनुपात की गणना करने के लिए उन्हें वर्गित किया जाता है, तो अंतर स्पष्ट हो जाता है, यानी 1.1²/1.2² = 85%, जो बिजली बिलों पर 15% की बचत का अनुवाद करता है।

DDR5 द्वारा शुरू किए गए वास्तुशिल्प परिवर्तन बैंडविड्थ दक्षता और उच्च स्थानांतरण दरों को अनुकूलित करते हैं, हालांकि, इन संख्याओं को सटीक अनुप्रयोग वातावरण को मापने के बिना निर्धारित करना मुश्किल है जिसमें प्रौद्योगिकी का उपयोग किया जाता है।लेकिन फिर भी, बेहतर वास्तुकला और उच्च स्थानांतरण दर के कारण, अंतिम उपयोगकर्ता डेटा के प्रति बिट ऊर्जा में सुधार का अनुभव करेगा।

इसके अलावा, DIMM मॉड्यूल वोल्टेज को स्वयं भी समायोजित कर सकता है, जो मदरबोर्ड की बिजली आपूर्ति के समायोजन की आवश्यकता को कम कर सकता है, जिससे अतिरिक्त ऊर्जा-बचत प्रभाव प्रदान किया जा सकता है।

डेटा केंद्रों के लिए, एक सर्वर कितनी बिजली की खपत करता है और कितनी कूलिंग लागत चिंता का विषय है, और जब इन कारकों पर विचार किया जाता है, तो अधिक ऊर्जा-कुशल मॉड्यूल के रूप में DDR5 निश्चित रूप से अपग्रेड करने का एक कारण हो सकता है।

त्रुटि सुधार

DDR5 में ऑन-चिप त्रुटि सुधार भी शामिल है, और जैसे-जैसे DRAM प्रक्रियाएं सिकुड़ती जा रही हैं, कई उपयोगकर्ता एकल-बिट त्रुटि दर और समग्र डेटा अखंडता को बढ़ाने के बारे में चिंतित हैं।

सर्वर अनुप्रयोगों के लिए, ऑन-चिप ईसीसी डीडीआर5 से डेटा आउटपुट करने से पहले रीड कमांड के दौरान सिंगल-बिट त्रुटियों को ठीक करता है।यह सिस्टम पर लोड को कम करने के लिए सिस्टम सुधार एल्गोरिदम से कुछ ईसीसी बोझ को डीआरएएम पर लोड करता है।

DDR5 त्रुटि जाँच और स्वच्छता का भी परिचय देता है, और यदि सक्षम किया जाता है, तो DRAM डिवाइस आंतरिक डेटा को पढ़ेंगे और सही डेटा को वापस लिखेंगे।

संक्षेप

जबकि DRAM इंटरफ़ेस आमतौर पर पहला कारक नहीं है जिस पर डेटा सेंटर अपग्रेड लागू करते समय विचार करता है, DDR5 पर करीब से नज़र डालने की ज़रूरत है, क्योंकि तकनीक प्रदर्शन में काफी सुधार करते हुए बिजली बचाने का वादा करती है।

DDR5 एक सक्षम तकनीक है जो शुरुआती अपनाने वालों को भविष्य के कंपोजेबल, स्केलेबल डेटा सेंटर में सहजता से स्थानांतरित करने में मदद करती है।आईटी और बिजनेस लीडर्स को DDR5 का मूल्यांकन करना चाहिए और यह निर्धारित करना चाहिए कि अपनी डेटा सेंटर परिवर्तन योजनाओं को पूरा करने के लिए DDR4 से DDR5 पर कैसे और कब माइग्रेट करना है।

पोस्ट करने का समय: दिसंबर-15-2022